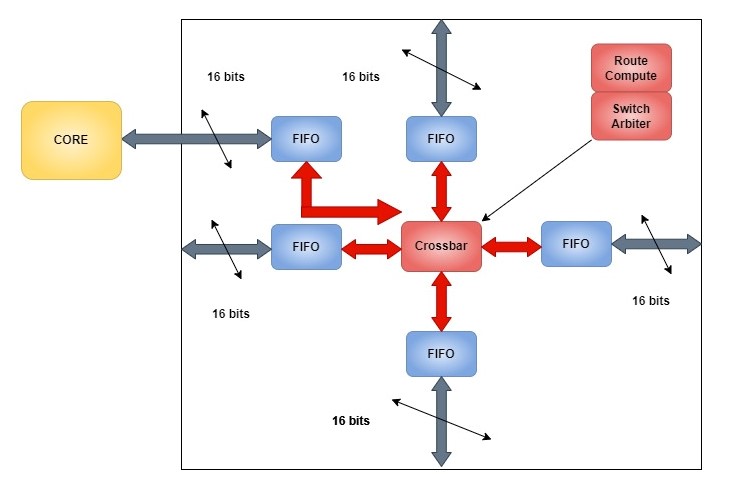

This repository contains the Verilog codes of the four main components of a 5-port NoC (Network-on-Chip) Router namely Core, FIFO buffer, Route Computing, and Switch Arbiter. This code was implemented and simulated on EDA Playground.

The specifications and functionalties of the NoC Router:

-

The NoC router has 5 ports namely Local, East, West, North, South.

-

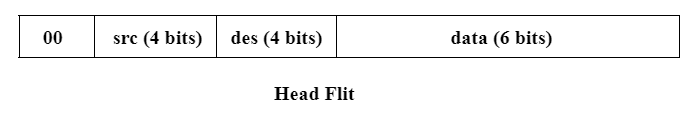

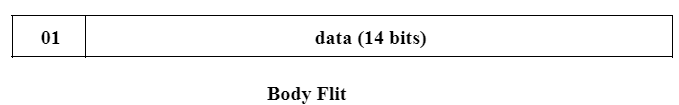

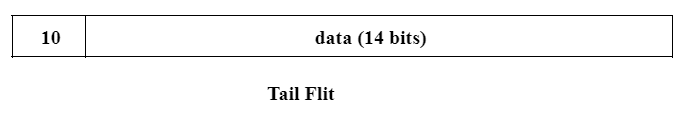

The Core is an FSM which breaks down the incoming data and generate flits (here of size 16 bits).

-

Here, the "src" and "des" represent the source and destination router respectively.

-

In the Core design code, I have parameterized the number of flits as 'n'.

-

FIFO (First-In-First-Out) Buffer is a read/write memory array that collects the generated flits and reads the flits out in the same order to the Crossbar.

-

The FIFO has k+1 entries (as parameterized in the FIFO design code) with 16 bits wide.

-

The Crossbar will transfer the flits from one FIFO buffer to another on the basis of Route Compute and Switch Arbiter Unit.

-

The Route Compute Unit determines the output port of a flit on the basis of its destination address. I have used XY Routing algorithm.

-

The Switch Arbiter Unit (here the arbitration policy is Round Robin) gives equal amount of clock cycles as priority for each and every FIFO buffer on a circular basis thus effectively balancing the load.

-

In the Switch_Arbiter design code, I have parametrized the number of clock cycles as 'm'.